TSMC เตรียมเริ่มทดสอบสายการผลิตชิปขนาด 2 นาโนเมตรในช่วงสัปดาห์หน้า ณ โรงงานเป่าซาน ไต้หวัน โดยได้เริ่มติดตั้งเครื่องจักร และชิ้นส่วนสำหรับการทดสอบผลิตเป็นที่เรียบร้อยแล้วในช่วงไตรมาส 2 ที่ผ่านมา เบื้องต้นได้ตั้งเป้าผลิตให้ได้ Yield Rate นิ่ง ๆ (อัตราการผลิตสำเร็จ) ก่อนจะเริ่มผลิตแบบ Mass Production ในปี 2025

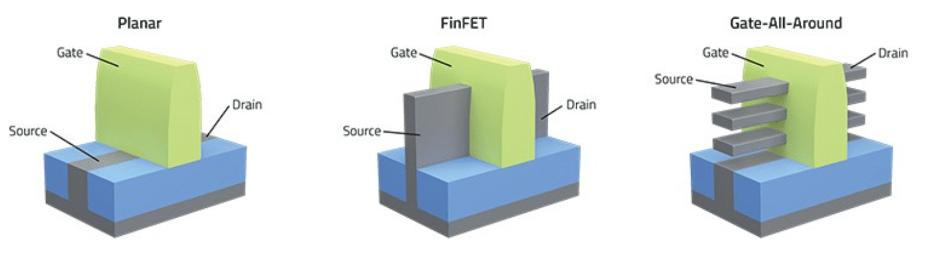

ชิปขนาด 2 นาโนเมตรของ TSMC คาดว่าจะใช้วิธีการผลิตแบบ Gate All Around ที่ทำให้สามารถอัดทรานซิสเตอร์ได้จำนวนมากขึ้น ในพื้นที่ที่เล็กลง ซึ่งจะช่วยให้สามารถโอนถ่ายข้อมูลได้รวดเร็วขึ้น และประหยัดพลังงานมากกว่าเดิม

ในตอนนี้สิ่งที่สำคัญที่สุดในช่วงแรกของการทดสอบของ TSMC คือการทำให้อัตราการผลิตสำเร็จมีความเสถียรมากที่สุด เพื่อจัดส่งให้กับลูกค้ารายใหญ่ที่สุดอย่าง Apple ได้ทันเวลา และไม่ไปซ้ำรอยกับเหตุการณ์ชิป 3nm ในช่วงแรก ที่ทำ Yield Rate ได้ที่ราว ๆ 50% เท่านั้น

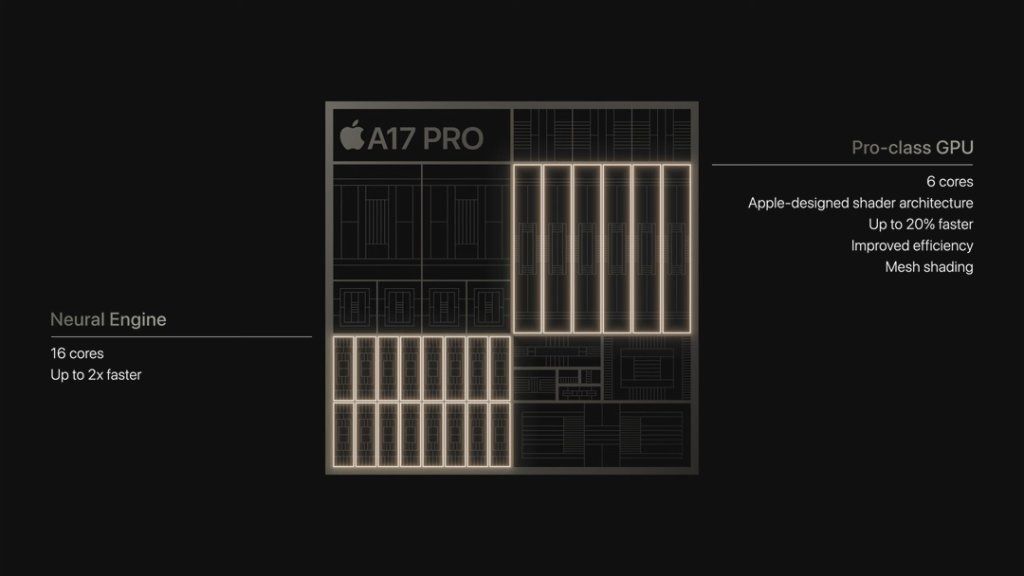

Apple คาดว่าจะเป็นลูกค้ารายแรกที่ได้ชิปเซตขนาด 2nm ไปได้มากที่สุด หรืออาจเป็นจำนวนทั้งหมดที่ TSMC ผลิตได้ โดยจะนำมาใช้กับชิป Apple A18 บน iPhone 17 เป็นรุ่นแรก และคาดว่าจะเพิ่มความเร็วในการประมวลผลเมื่อเทียบกับชิป 3nm ถึง 10 – 15% และลดการใช้พลังงานได้ถึง 30%

Comment